July 1998-2

The XRT8000 device can be configured to generate either a T1 (1.544MHz) or E1 (2.048MHz) rate clock signal, from a "Reference Clock signal of frequency 8kHz. The approach that one should use to accomplish all of this is presented below.

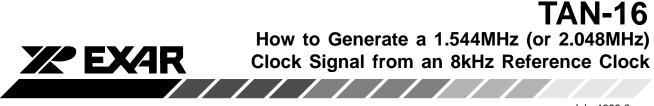

1. To generate a 1.544MHz clock signal, from an 8kHz clock signal:

# Figure 1. Illustration of the XRT8000 device generating a 1.544MHz clock signal from an 8kHz Reference clock signal (Reverse/Slave Mode).

In order to configure the XRT8000 device to operate in this manner, the user must configure the chip to operate in the "Reverse/Slave" Mode. The user accomplishes this by executing the following steps:

\* Pull the MSB pin (pin 8) "low".

Rev. 1.00

This will configure the device to operate in the "Slave" Mode.

\* Write the following values, into the corresponding "Configuration Registers", (via the Microprocessor Serial Interface) as tabulated below in Table 1.

**EXAR** Corporation, 48720 Kato Road, Fremont, CA 94538 · (510) 668-7000 · FAX (510) 668-7017

| Step<br>Number | Configuration<br>Register | Value<br>(to be written) | Comments                                                                                                                                                                                                                |

|----------------|---------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | CR1                       | 01101                    | The first four bits (e.g., "0110") configures<br>the chip to operate in the "Reverse" Mode.<br>Further, it configures each of the PLLs to<br>generate a 1.544 MHz clock signal.                                         |

|                |                           |                          | Setting the fifth bit to "1", enables PLL #1.<br>If one does not wish to generate the<br>1.544 MHz clock via pin 6, then one should<br>set this bit to "0".                                                             |

| 2              | CR2                       | 00001                    | This step simply enables PLL #2 to<br>output a 1.544 MHz clock via the "CLK2"<br>output pin (pin 13). If one does not wish<br>to output any signal via this pin, then he/<br>she should write "00000" to this register. |

| 3              | CR3                       | xxxxx                    | This step can be skipped                                                                                                                                                                                                |

| 4              | CR4                       | xxxxx                    | This step can be skipped                                                                                                                                                                                                |

| 5              | CR5                       | 11100                    | This step enables the XRT8000 to output<br>the 8kHz output via the SYNC output pin<br>(pin 2), and the PLL_1 and PLL_2 outputs<br>via the CLK1 (pin 6) and CLK2 (pin 13)<br>output pins, respectively.                  |

### Table 1. Programming Procedure, via the Microprocessor Serial Interface

By executing the above-mentioned procedure, the XRT8000 device will be configured to operate in the "Forward/Slave" Mode, and will generate a 2.048MHz clock via the CLK1 and CLK2 output pins, when receiving an 8kHz signal at the  $F_{IN}$  input pin (pin 3).

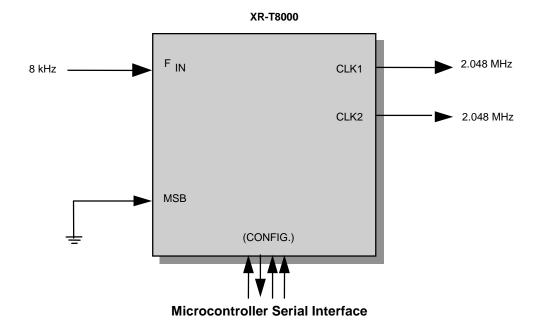

2. To generate a 2.048MHz clock signal, from an 8kHz clock signal:

# Figure 2. Illustration of the XRT8000 device generating a 2.048MHz clock signal from an 8 kHz Reference clock signal (Reverse/Slave Mode).

In order to configure the XRT8000 device to operate in this manner, the user must configure the chip to operate in the "Forward/Slave" Mode. This user accomplishes this by executing the following steps:

\*Pull the MSB pin (pin 8) "low".

This will configure the device to operate in the "Slave" Mode.

\*Write the following values, into the corresponding "Configuration Registers", (via the Microprocessor Serial Interface) as tabulated below.

**TAN-16**

| Step<br>Number | Configuration<br>Register | Value<br>(to be written) | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------|---------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | CR1                       | 00101                    | The first four bits (e.g., "0010")<br>figures the chip to operate in the<br>"Forward" Mode. Further, it configures<br>each PLL to generate a "k x 64" clock<br>signal.                                                                                                                                                                                                                                                                                                                       |

|                |                           |                          | <b>Note:</b> The value for "k" is specified in Step # 3.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                |                           |                          | Setting the fifth bit to "1", enables PLL # 1.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                |                           |                          | If one does not wish to generate the<br>2.048 MHz clock<br>via pin 6, then one should set this bit<br>to "0".                                                                                                                                                                                                                                                                                                                                                                                |

| 2              | CR2                       | 00001                    | This step simply enables PLL #2 to<br>output a 2.048 MHz clock via the<br>"CLK2" output pin (pin 13).<br>If one does not wish to output any<br>signal via this pin, then he/she should<br>write "00000" to this register.                                                                                                                                                                                                                                                                    |

| 3              | CR3                       | 11111                    | This step sets the value for "k" for PLL<br># 1 (see "Comments" for "Step 1") to<br>32. Consequently, the XRT8000<br>will generate a clock signal of<br>2.048 MHz.                                                                                                                                                                                                                                                                                                                           |

| 4              | CR4                       | 11111                    | This step sets the value for "k" for PLL<br># 2 (see "Comments" for "Step 1") to<br>32.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5              | CR5                       | 11100                    | This step enables the XRT8000 to<br>output the 8kH output via the SYNC<br>output pin (pin 2), and the PLL_1<br>and PLL_2 outputs via the CLK1 (pin<br>6) and CLK2 (pin 13) output pins,<br>respectively. By executing the above-<br>mentioned procedure, the XRT8000<br>device will be configured to operate in<br>the "Forward/Slave" Mode, and will<br>generate a 2.048 MHz clock via the<br>CLK1 and CLK2 output pins, when<br>receiving an 8 kHz signal at the FIN<br>input pin (pin 3). |

#### Table 2. Programming Procedure, via the Microprocessor Serial Interface

Rev. 1.00

By executing the above-mentioned procedure, the XRT8000 device will be configured to operate in the "Forward/Slave" Mode, and will generate a 2.048 MHz clock via the CLK1 and CLK2 output pins, when receiving an 8 kHz signal at the FIN input pin (pin 3).

#### NOTICE

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contained here in are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for in accuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately protected under the circumstances.

Copyright 1998 EXAR Corporation Datasheet July 1998 Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.